Commit Stage

Part of the Extended Instruction Pipeline .

-

Instructions are only allowes the change the architectual state in the commit stage.

-

Resources of instructions are freed

-

Commits always happen in program order, even in Out-Of-Order Execution Processors

-

Speculative instructions can’t commit until it is verified that they should have been executed

-

On x86 with mutliple uops (see CISC decoding ) a instruction commits if all uops have completed

- In some cases partial commits are allowed

Recovery from Exceptions #

- Exceptions are handled in commit, since they should only be executed if they are not speculative; Commit stage is the correct stage for that.

- Steps:

- Flush all instructions in flight

- Recover from the speculative state of the execution of the instruction that triggered the exception

- Redirect front end to the exception handler

Recovery from Branch Misprediction #

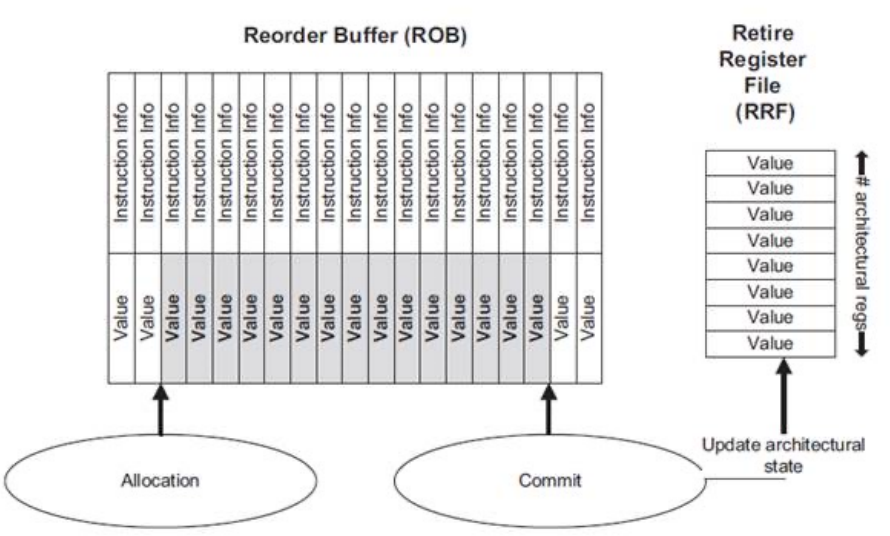

Retire Register File (RRF) #

-

When an instruction of the reorder buffer commits its value is final and put into the Retire Register File (RRF).

-

In that case all consumers waiting for that value should be updated

-

All instructions in the issue need to be checked Reorder Buffer (ROB) ID needs to be chenged to the architectual register

-

Nothing else to be done, new instuctions fetch data from the RRF; Instructions in the issue queue copied it due to the wakeup signal

In combination with the Merged Register File #

-

Nothing to be done, speculative as well as final values are in the MRF.

-

nothing to be done

-

registers are not moved, nothing to be done

-

Register reclamation is more complicated -> Register can only be freed if another instruction commits that writes to the same logical register