Instruction Cache

or ICache. Kind of CPU Cache usually only in level 1, with little different requirements. Instructions share the same cache as data from level 2 and upwards.

-

Low latency very important, in case of failed Branch Prediction , the correct branch has to be fetched ASAP

-

Conflict misses are not (so much) expected due to linear access behavour of instruction flow

-

ICache can return the whole cacheline to the Instruction Fetch stage.

-

ICache can be a blocking cache (no benefit if it was non-blocking)

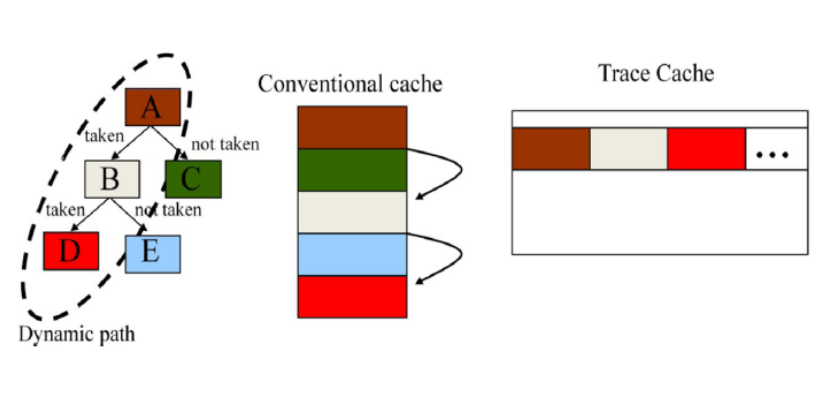

Trace Cache #

Fill the ICache with instructions of a predicted instruction trace (execution). This works in combination with a Branch Prediction .

New traces are started when misprediction happens

- Advantage: Better use of cache space, higher effective bandwidth

- Disadvantage: more compilcated logic

- How does the cpu then know where to jump on jump instructions? Since now the instructions are no longer in the order they were