Instruction Decode Stage

Part of Instruction Pipelining .

RISC decoding #

- Fixed instruction length makes identifying instructions easier

- Instructins are simple: only generate few control signals in the pipleine

- RISC decoder can be programmed with simple programmable logic array or look-up tables

CISC decoding #

- Have to be translated on the fly

- Single CISC instruction can represent mulitiple RISC instructions:

;; CISC

add [eax], ebx

;; RISC

load r0, ds:[eax]

add r1, r0, ebx

store ds:[eax], r1

-

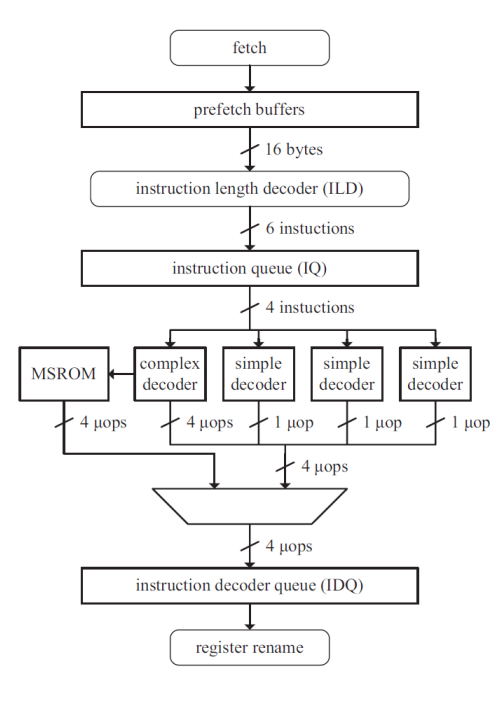

To handle this complexity, modern x86 processors translate CISC instructions into RISC-like microoperations (uops)

-

Also contains Loop Stream Detector

Instruction length decode (ILD) #

- Identifies instructions

- Decodes prefixed

- Common instructions handled in one cycle

- only length changing prefixes require 6 cycles

Dynamic translation #

- simple decoder: simple instructins -> produces single uops

- complex decoder -> leads up to 4 uops