Instruction Set Architecture

- “Interface from the programmer to the processor”

- Processors are binary compatible if they support the same ISA

Data Types and formats #

- Integer types

- Fixed / Floating point types

- String formats

- …

Operands #

-

Number of operands (0, 1, 2, 3)

-

Types of operands

- Immediate operands (part of the instruction)

- Register operands (content of the register is the operand)

- Memory operands (content of a memory address is the operand)

-

Alignment of operands

- Memory operand is aligned at a n-bit boundary if the address is a multiple of n

- Usually memory operands have to be aligned according to their own size

- Can be required by the ISA to only access size-aligned data

-> Needed for cache lines: If cach lines are

byte sized and aligned, for a reasonably large

, then smaller data will always fit in a cache line if it is also aligned.

Addressing modes #

- Immediate operands (part of the instruction)

- Register operands (content of the register is the operand)

- Direct (memory address is part of the instruction)

- Only if you know the address of a constant or something in the data segment

- Register indirect: (memory address is in a register)

- Indexed: (register indirect plus fixed offset)

- Can be used for PC-relative jumps (maybe for jump tables like for

switchstatements?)

- Can be used for PC-relative jumps (maybe for jump tables like for

Classes of Instructions #

- data transfer

- arithmetic and logic operations

- control flow: calls, jumps, …

- I/O instructions

- System level instructions: interrupts, stack, priviledge level

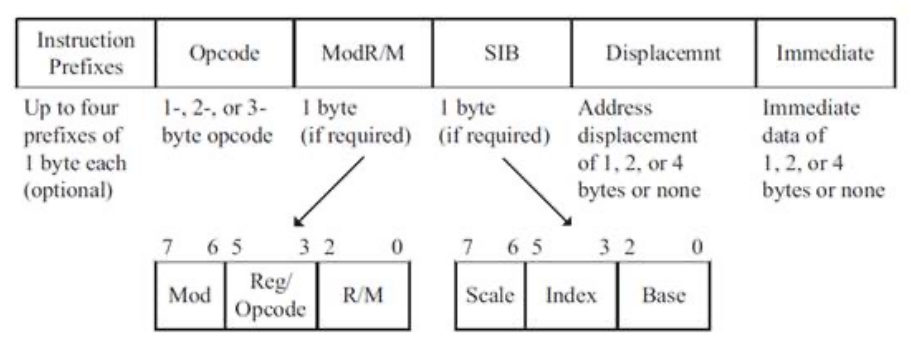

Instruction format #

- structure of opcode and operands

- either single format for all instructions (Von Neumann Architecture )

- or more flexible ones (complex decoding)

- (NOTE: instruction size depends on operand types (registers really small, memory address much bigger))

Registers #

-

Memory in the processor

-

Fast access (fastest access)

-

Types:

- General registers: interges, addesses

- Floating point registers

- Special refisters: multimedia, loop control register, …

- System registers: program counter, status, control register

-

Only few registers defined by ISA to keep names as short as possible

-

Register file = set of (same type) registers

-

Sliding window register file:

- Attempt to have a lot of registers, but still have instuction length short:

- Have a “Window” you can move over the full register file. All register access then only acts on the active window

- Special operations to slide the window of addresses over the real registers

- Attempt to have a lot of registers, but still have instuction length short:

Execution Modes #

-

Motivation: Applications and data need to be protected from other running programs

-

OS manages hardware -> Assigns memory ranges to processes

-

Two execution modes:

- Supervisor mode:

- Reserved for OS

- Full access to all components

- Can modyfiy virtual address table

- User mode:

- Limited access

- Access to memory only through memory translations (Virtual address space)

- No priviledged instruction for I/O or accerss to control registers

- Supervisor mode:

Exception Handling #

-

Exception (Interrupt) triggered by the program

- Executing a priviledged instruction in user mode

- Division by Zero

- Access virtual page with wrong permissions

-

Exception handled by the OS:

- Interrupt the currently executed instruction

- save processor state (all registers and immediate values)

- jump to handler for the exception

- switch to supervisor mode

- handle the exception

- return to original instruction in user mode

-

Precise exceptions:

- Assume all previous instructions are complete

- Assume no future instructions have been exectuted

- Assumes no piplining

-

Imprecise exceptions:

- Exceptions can happen out of order

CISC vs RISC #

- CISC

- Complex instruction set architecture

-

variable instuction format

-

Instructions can have prefixes

- Opcode can start in the first 5 bytes

-

memory and register operands

-

specialized instuctions

-

- RISC

- Complex instruction set architecture

- single instruction format (fetch / decode simpler)

- load/store architecture

- limited addressing modes

- one cycle machine instructions

Comparison - CISC leads to shorter programs - CISC is more flexible - RISC is faster - RISC needs to emulate more complex instuctions

Endianness #

- Order of the bytes

- least significant byte first

- most significant byte first